EP1C6Q240C8N IC FPGA 185 I/O 240QFP

Parameter sa Produkto

Deskripsyon

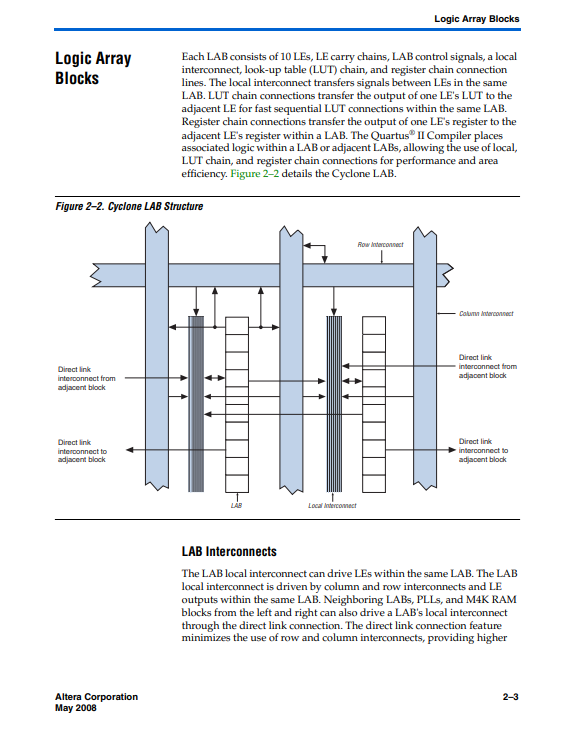

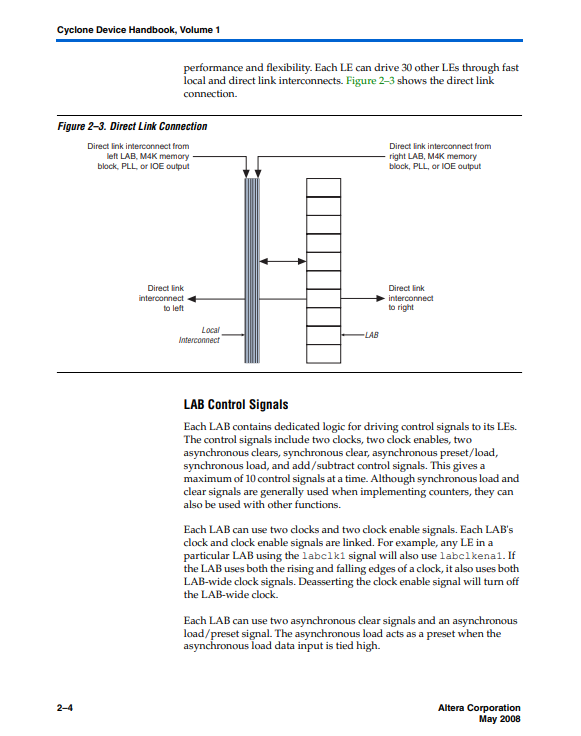

Ang Cyclone® device adunay duha ka dimensiyon nga row- ug column-based nga arkitektura aron ipatuman ang custom logic.Ang mga kolum ug row nga mga interconnect sa lain-laing mga katulin naghatag og signal interconnects tali sa LABs ug embedded memory blocks.Ang logic array naglangkob sa mga LAB, nga adunay 10 ka LE sa matag LAB.Ang LE usa ka gamay nga yunit sa lohika nga naghatag episyente nga pagpatuman sa mga gimbuhaton sa lohika sa gumagamit.Ang mga LAB gigrupo sa mga laray ug mga kolum sa tibuuk nga aparato.Ang cyclone device nagsangkad tali sa 2,910 ngadto sa 20,060 LEs.Ang mga bloke sa M4K RAM tinuod nga mga bloke sa memorya sa dual-port nga adunay 4K bits sa memorya plus parity (4,608 bits).Kini nga mga bloke naghatag ug gipahinungod nga tinuod nga dual-port, simple nga dual-port, o single-port nga memorya hangtod sa 36-bits ang gilapdon hangtod sa 250 MHz.Kini nga mga bloke gi-grupo sa mga kolum sa tibuuk nga aparato taliwala sa pipila nga mga LAB.Ang mga cyclone device nagtanyag tali sa 60 hangtod 288 Kbits nga naka-embed nga RAM.Ang matag Cyclone device I/O pin gipakaon sa usa ka I/O element (IOE) nga nahimutang sa mga tumoy sa LAB row ug column sa palibot sa periphery sa device.Ang I/O pins nagsuporta sa nagkalain-laing single-ended ug differential I/O standards, sama sa 66- ug 33-MHz, 64- ug 32-bit PCI standard ug ang LVDS I/O standard hangtod sa 640 Mbps.Ang matag IOE adunay usa ka bidirectional I/O buffer ug tulo ka mga rehistro alang sa pagparehistro sa input, output, ug output-enable signals.Ang dual-purpose nga DQS, DQ, ug DM nga mga pin kauban ang mga delay chain (gigamit sa phase-align nga mga signal sa DDR) naghatag suporta sa interface sa mga external memory device sama sa DDR SDRAM, ug FCRAM nga mga device hangtod sa 133 MHz (266 Mbps).Ang mga cyclone device naghatag ug global clock network ug hangtod sa duha ka PLL.Ang global nga network sa orasan naglangkob sa walo ka global nga linya sa orasan nga nagmaneho sa tibuuk nga aparato.Ang global nga network sa orasan makahatag ug mga orasan para sa tanang mga kahinguhaan sulod sa device, sama sa IOEs, LEs, ug memory blocks.Ang mga linya sa orasan sa kalibutan mahimo usab nga magamit alang sa mga signal sa pagkontrol.Ang Cyclone PLLs naghatag og general-purpose clocking nga may clock multiplication ug phase shifting ingon man mga external outputs para sa high-speed differential I/O nga suporta.

| Mga detalye: | |

| Hiyas | Bili |

| Kategorya | Mga Integrated Circuit (ICs) |

| Naka-embed - Mga FPGA (Field Programmable Gate Array) | |

| Si Mfr | Intel |

| Sunod-sunod nga | Cyclone® |

| Pakete | Tray |

| Kahimtang sa Bahin | Karaan na |

| Gidaghanon sa mga LAB/CLB | 598 |

| Gidaghanon sa Logic Elements/Cell | 5980 |

| Kinatibuk-ang RAM Bits | 92160 |

| Gidaghanon sa I/O | 185 |

| Boltahe - Supply | 1.425V ~ 1.575V |

| Type sa Pag-mount | Ibabaw nga Mount |

| Operating Temperatura | 0°C ~ 85°C (TJ) |

| Pakete / Kaso | 240-BFQFP |

| Supplier Device Package | 240-PQFP (32x32) |

| Numero sa Base nga Produkto | EP1C6 |

May kalabotanMGA PRODUKTO

-

Ang Tel

-

E-mail

-

skype

-

whatsapp

whatsapp